Advantages

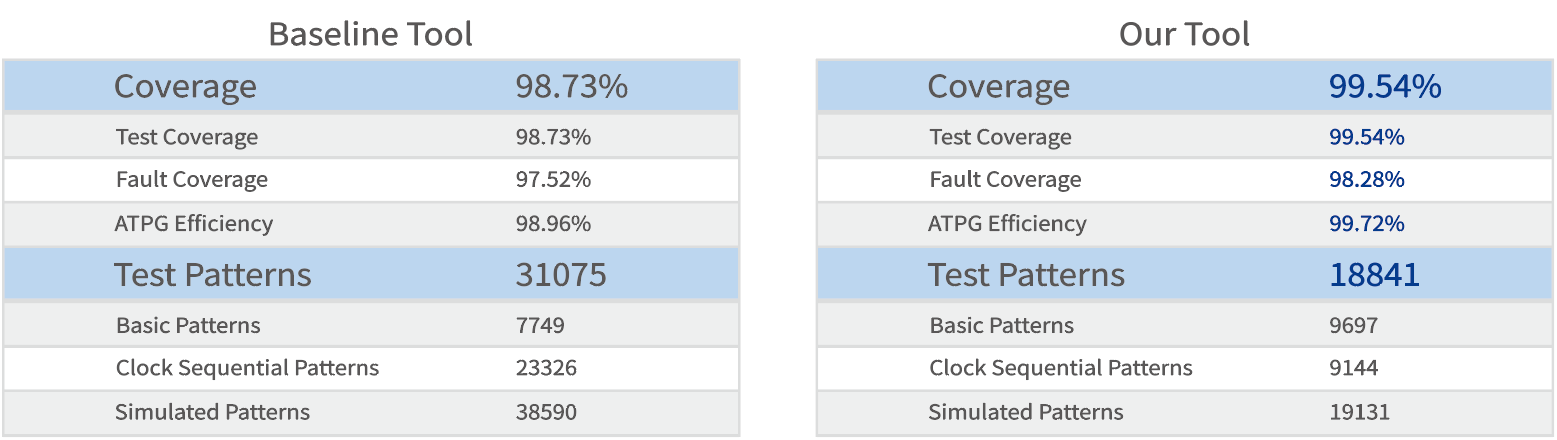

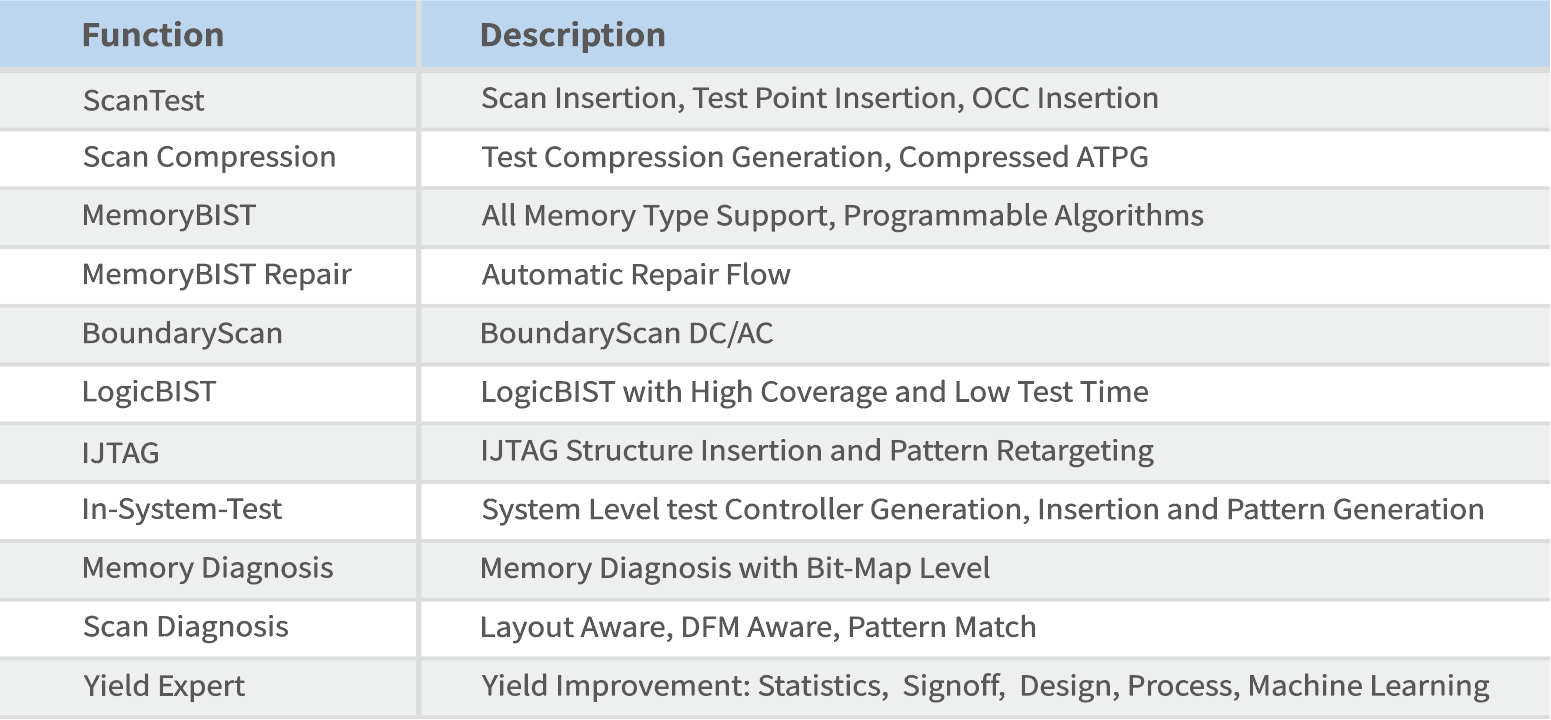

- DFTEXP covers a complete suite of DFT EDA tools and supports the implementation of DFT designs for chips across various fields, including MCU, AI, GPU, NetWork, 5G Baseband, and AP. It supports In-System-Test and functional safety testing for automotive devices.

- DFTEXP provides a comprehensive yield diagnostics and enhancement solution that can adapt to different processes and fab requirements. It helps locate root causes of yield issues and establish yield enhancement solutions through the DFT Diagnosis and DATAEXP system.

- By integrating DFT diagnostic results with chip-related data from DATAEXP-YMS, such as product layout, WAT, CP, and FT data, inline data, equipment, and defect data, DFTEXP allows for more accurate fault detection and yield issues root cause identification, accelerating the time-to-market cycle for chip products.

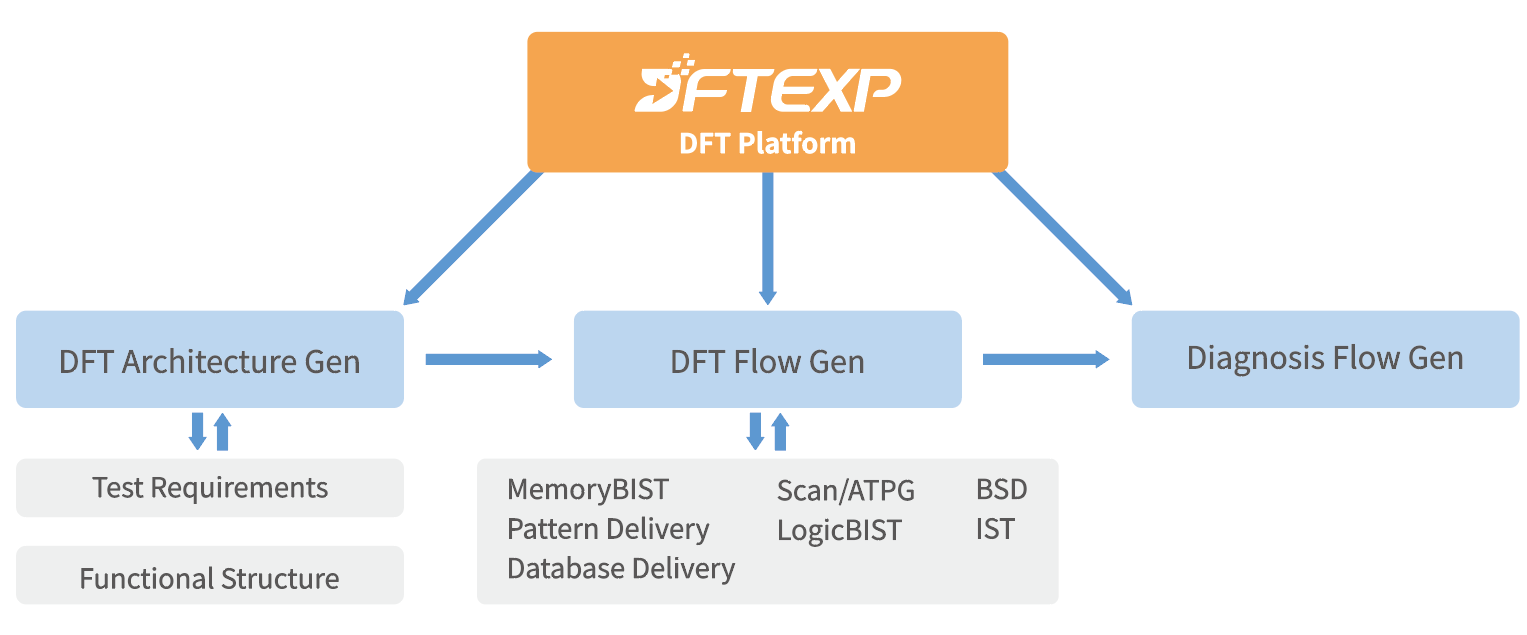

- DFTEXP features an automated DFT implementation flow and a comprehensive wafer acceptance flow. It supports both RTL and Netlist Flow and accelerates the time-to-market cycle for products through hierarchical DGT and hierarchical ATPG flows. DFTEXP helps establish a comprehensive wafer acceptance flow to meet the DPPM requirements of various chip designs.